### https://www.j-platpat.inpit.go.jp/

### **PNPN junction Transistor type Pinned Photodiode**

Visit https://www.j-platpat.inpit.go.jp/ and put the patent number 1975-134985

| File 1975-13<br>Public 1975-05 | Dublia | 1975/11/10<br>1977/05/13<br>1983/10/19 |

|--------------------------------|--------|----------------------------------------|

|--------------------------------|--------|----------------------------------------|

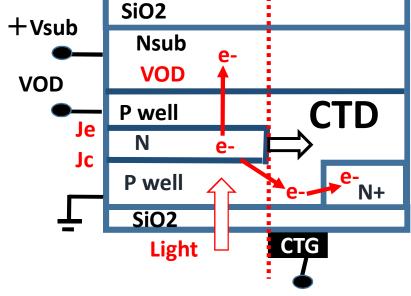

(1)半導体基体 (Nsub) に、第1 電導型の第1 半導体領域 (P well) と、(2) 之の上に形成された 第2導電型の第2半導体領域 (N) とが 形成されて (3) 光感知部 (N) と 之よりの電荷を転送する電荷 転送部 (CTD)とが (4)上記半導体基体 (Nsub) の主面に沿う如く配置されて成る(5)固体撮像 装置に於いて、上記光感知部 (N)の上記第2 半導体領域 (N)に 整流性接合(Je)が形成され、 該接合(Je)をエミッタ接合とし、(6)上記第1 (P well)及び第2半導体領域 (N) 間の接合を コレクタ接合(Jc)とする (PNP)トランジスタを形成 し(7) 該トランジスタのベースとなる上記第2半 導体領域(N)に光学像に応じた電荷を蓄積し ここに蓄積された電荷を上記転送部(CTD)に 移行させてその転送を行うようにしたことを特徴 とする固体撮像装置。

### **PNPN junction Transistor type Pinned Photodiode**

Visit https://www.j-platpat.inpit.go.jp/ and put the patent number 1975-134985

| File<br>Public | 1975-134985<br>1975-058414 | Filed<br>Public<br>Grant | 1975/11/10<br>1977/05/13<br>1983/10/19 |  |  |

|----------------|----------------------------|--------------------------|----------------------------------------|--|--|

|                |                            |                          |                                        |  |  |

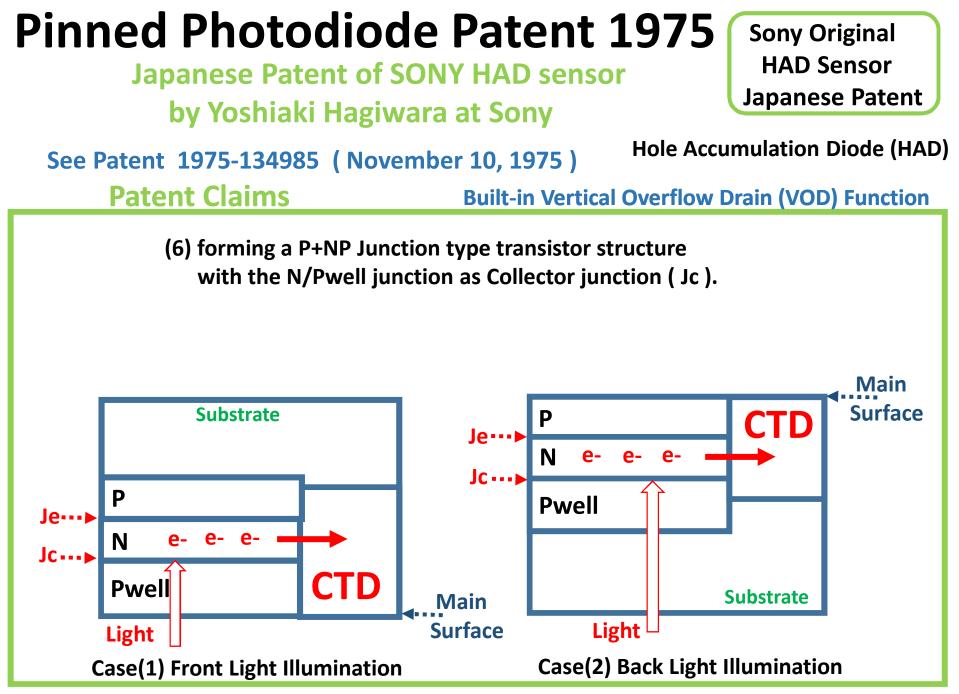

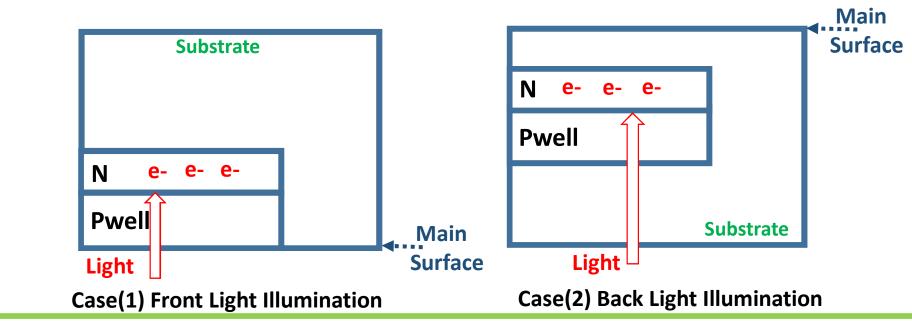

Patent Claim in English Translation

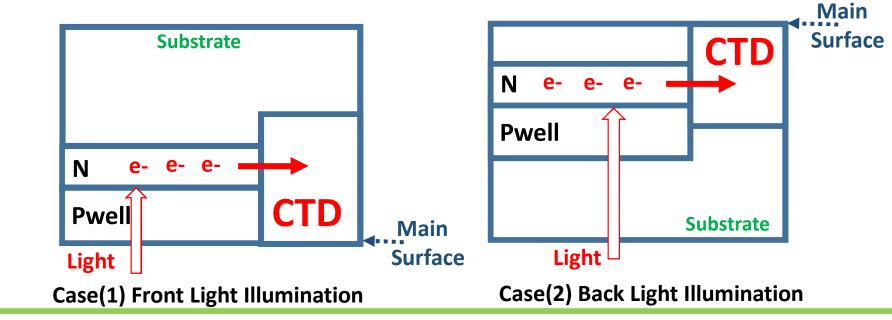

(1) In the semiconductor substrate (Nsub), the first region(P well) of the first impurity type is formed, (2) on which, the second region (N) of the second impurity type is formed. (3) The charge (e-) from the light collecting part (N) is is transferred to the adjacent charge transfer device (CTD). (4) Both are placed along the main surface of the semiconductor substrate. (5) In the solid stare image sensor so defined, a rectifying Emitter junction (Je) is formed on the second region (N) of the light collecting part (N). And (6) Collector junction (Jc) is formed by the second region (N) and the first region (P well), forming a (PNP) transistor structure, (7) Photo charge is stored in the Base (N) according to illuminated light intensity and transferred to the adjacent CTD. The solid state image sensor so defined is in the scope of this patent claim.

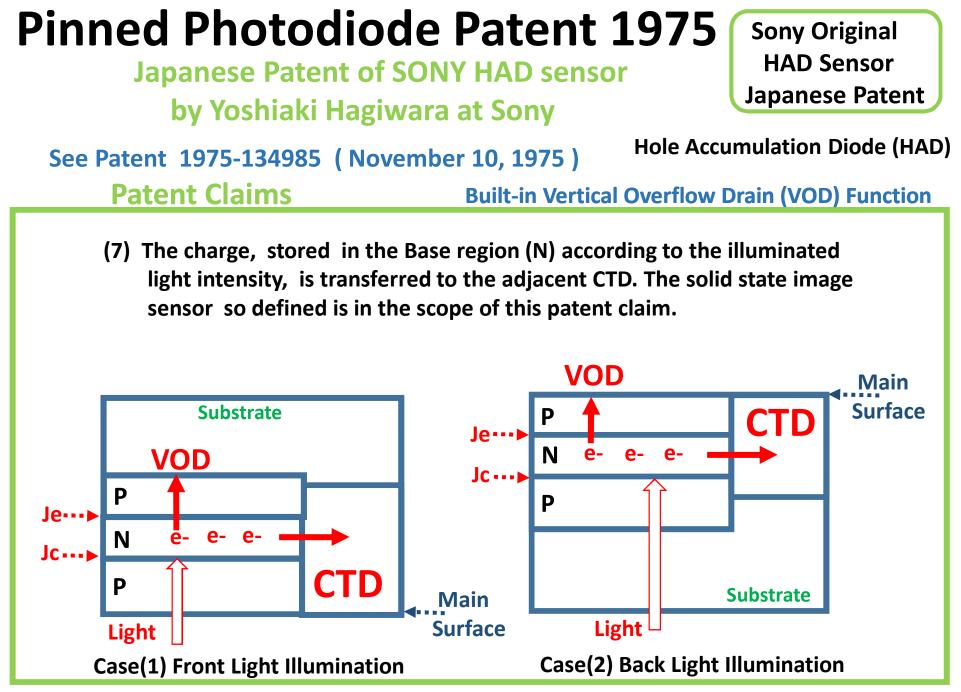

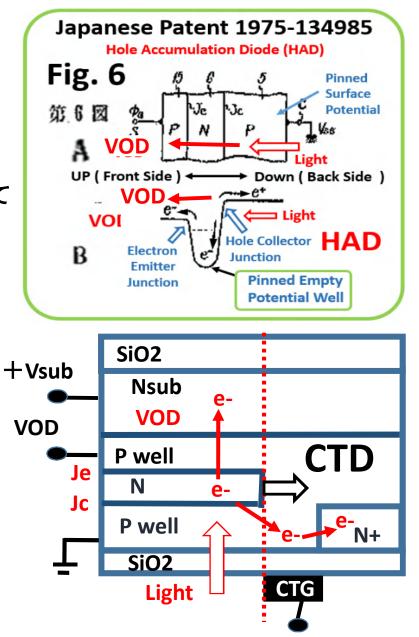

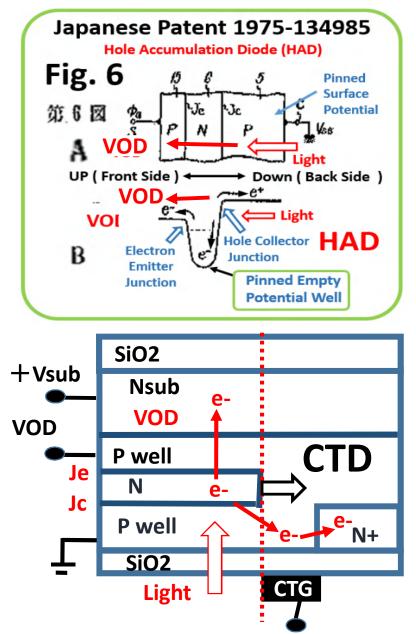

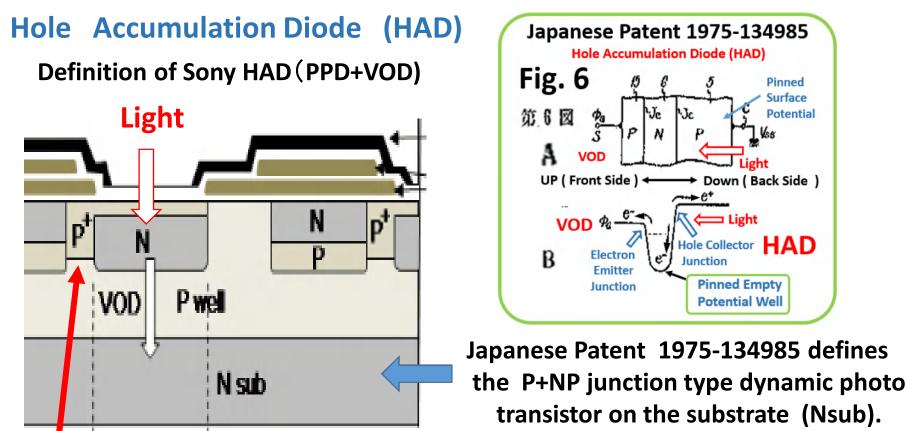

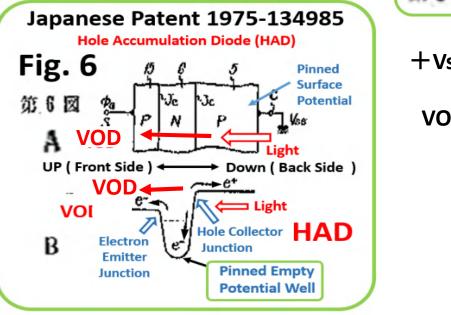

Fig.6 shows that this is also the invention of the in pixel VOD (vertical overflow drain).

# **Definition of Pinned Photodiode**

Surface Potential must be directly Pinned by the adjacent channel stop P+ region. Otherwise the surface P+ region becomes floating by the RC delay time. Though the surface P+ region can be connected by remote P+ channel stops, however, it will still have the RC delay time and will be floating and NOT pinned.

Pinned Photodiode must have the adjacent P+ channel Stops.

Japanese Patent 1975-134985 by Hagiwara at Sony on Oct 23, 1975.

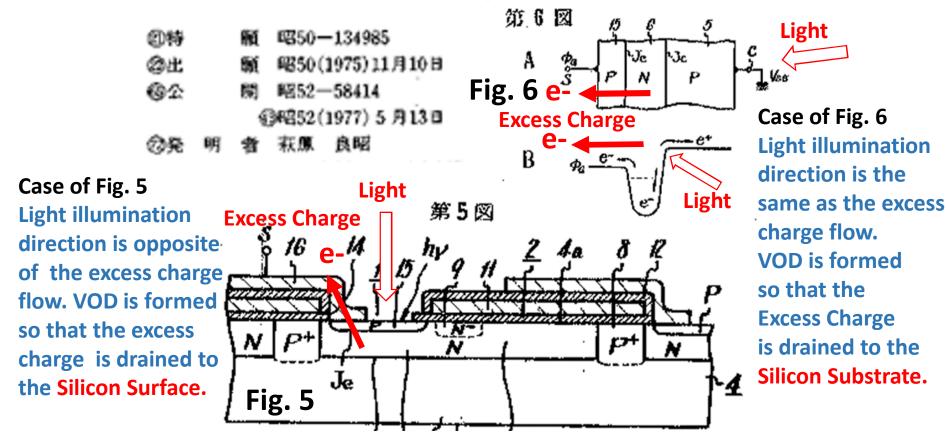

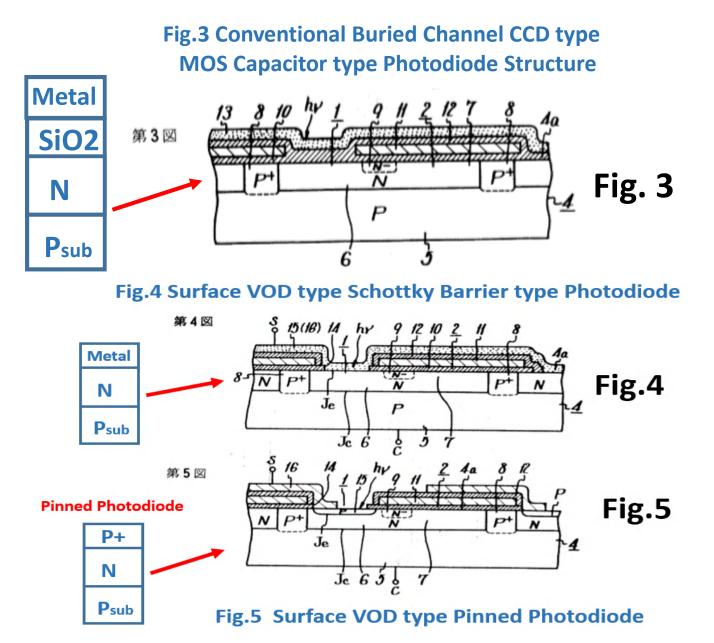

In case of Fig. 5, the P+NP junction type Pinned Photodiode with the surface P+ hole accumulation layer that has a fixed or Pinned surface potential by the external metal Ohmic contact. The Excess charge flow is toward the silicon surface in this case. Light illumination direction is the opposite as the excess charge flow in case of Fig. 5.

In case of Fig. 6, Light illumination direction is the same as the excess charge flow. The VOD is formed so that the excess charge is drained to the silicon substrate.

Visit https://www.j-platpat.inpit.go.jp/ and put the patent number 1975-134985

### <sup>12</sup>特許公報<sup>(B2)</sup>昭58-46905

#### ① 日本国特許庁(JP) ① 特許出願公告

### <sup>12</sup> 特許公報<sup>(B2)</sup> 昭58-46905

| ⑤Int.Cl. <sup>3</sup>       | 識別記号 | 庁内整理番号               | 2049公告 | 昭和58年(1983)10月19日 |

|-----------------------------|------|----------------------|--------|-------------------|

| H 04 N 5/30<br>H 01 L 27/14 |      | 6940—5 C<br>6819—5 F | 発明の数   | 佐 1               |

(全4頁)

|     |      |     | 1                  |    | 2                                               |

|-----|------|-----|--------------------|----|-------------------------------------------------|

| 铋固体 | 、撮偽  | 使装置 | Ē                  |    | 像装置は、第1図に示すように、夫々絵素となる<br>光感知部(センサー部)1が行(水平)及び列 |

| ②特  |      | 願   | 昭50—134985         |    | (垂直)方向に夫々複数個配列され、共通の列上                          |

| 22出 |      | 願貢  | 昭50(1975)11月10日    |    | の光感知部1に関し、共通の垂直シフトレジスタ                          |

| 65公 |      | 開   | 昭52—58414          | 5  | 2 が設けられている。この垂直シフトレジスタ2                         |

|     |      | 4   | 9昭52(1977)5月13日    |    | はCCDよりなり、その電荷転送部が、対応する                          |

| @発  | 明    | 者   | 萩原 良昭              |    | 列上の光感知部1に夫々隣合つて設けられる。又、                         |

|     |      |     | 横浜市保士ケ谷区狩場町 303 の  |    | 各シフトレジスタ2の一端(第1図に於いて下端)                         |

|     |      |     | 159 狩場台アパート 402 号室 |    | には水平シフトレジスタ3が設けられ、撮像光学                          |

| 创出  | 願    | 人   | ソニー株式会社            | 10 | 像に応じて各光感知部1に生じた電荷を、例えば                          |

|     |      |     | 東京都品川区北品川6丁目7番35   |    | テレビジョン映像に於いては、その帰線消去期間                          |

|     |      |     | 号                  |    | に於いて垂直シフトレジスタ 2の各転送部に転送                         |

| 创代  | 理    | 人   | 弁理士 伊藤 貞           |    | し、とのシフトレジスタ2によつてとの電荷を垂                          |

|     |      |     |                    |    | 直方向に順次シフトして水平シフトレジスタ3に                          |

| 674 | 非常午前 | 青求の | >範囲                | 15 | 転送し、更にこの水平シフトレジスタによつて各                          |

#### の特許請求の範囲

1 半導体基体に、第1導電型の第1半導体領域 と、之の上に形成された第2導電型の第2半導体 領域とが形成されて光感知部と之よりの電荷を転 送する電荷転送部とが上記半導体基体の主面に沿 う如く配置されて成る固体撮像装置に於いて、上 20 1とこれに隣合う垂直シフトレジスタ2の転送部 記光感知部の上記第2半導体領域に整流性接合が 形成され、該接合をエミツタ接合とし、上記第1 及び第2半導体領域間の接合をコレクタ接合とす るトランジスタを形成し、該トランジスタのペー スとなる上記第2半導体領域に光学像に応じた電 25 荷を蓄積し、ことに蓄積された電荷を上記転送部 に移行させて、その転送を行うようにしたことを 特徴とする固体撮像装置。

#### 発明の詳細な説明

チャンネル型CCDを用いた固体擦像装置に係わ 30

CCDを用いた固体擦像装置としてはフレーム トランスフア方式によるもの、或いはインターラ イントランスフア方式によるものが提案されてい 35 30

インターライントランスフア方式による固体撮

- 15 転送し、更にこの水平シフトレジスタによつて各 行の絵素に関する電荷を水平方向にシフトして出 力端子はよりこの電荷に応じた撮像信号を得るよ うになされている。

- このような構成による固体撮像装置の光感知部 の構造を第2図及び第3図に示す。この例に於い ては埋込みチャンネル型CCD構成とした場合で、 との場合、半導体基体4に、第1の導電型例えば P型半導体領域5と、これの上に基体4の一主面 4 a に臨んで第2の導電型例えばN型の半導体領 域6とが設けられ、主面4aに沿つて光感知部1 とこれに隣合つてシフトレジスタ2の各転送部7 が設けられてなる。8は領域5と同導電型のチャ ンネルストツバー領域で、各感知部1間、及び各 本発明は電荷転送素子(CCD)、特に埋込み 30 シフトレジスタ2間を互に分離するものであり、 9は領域6と同導電型を有するもこれより低い不 純物濃度を有し、光感知部1とこれに隣合うシフ トレジスタ2との間に設けられて両者間に電位障 壁を形成する為の領域である。

- 光感知部1及び転送部7上の、主面4a上には 例えばSiO。より成る絶縁膜10が被着される。 そして、これの上に各シフトレジスタ2に対し、

-133 -

#### ⑫特 許 公 報<sup>(B2)</sup> 昭58-46905

(2)

特公 昭58-46905

3

その共通の行上の転送部に関して共通に転送電極 11が延長被着され、この電極11上には同様に 例えばSiO2より成る絶縁膜12が被着され、こ れの上に跨いで特に光感知部1上を含んでいわゆ るセンサー電極13が被着される。この電極13 5 負の電位φαを与える。 は光透過性を有するネサ、或いは不純物が高濃度 をもつてドープされて導電性が付与された多結晶 シリコン層より構成される。

このような構成による固体撮像装置の光感知部 絶縁膜10を通じて与えるので、特に短波長側に おける感度が低くなる欠点がある。

本発明は上述した欠点を改善した固体撮像装置 を提供せんとするものである。

第4図及び第5図を参照して本発明を説明する。15 之等第4図、第5図に於いて、第2図及び第3図 と対応する部分には同一符号を付して重複説明を 省略する。

本発明に於いては、光感知部1上の少なくとも 受光領域上の絶縁膜10及び12を除去し、窓 14を形成すると共に、光感知部1の半導体領域 6上に主面4aに臨んで整流性接合Je を形成す る。この接合Je は例えば第4図に示す如く領域 6と異なる導電型即ちP型の不純物がドープされ 4

固定電位、即ち例えば接地電位を与える。一方、 受光期間即ちシフトレジスタ2に於ける転送期間 中にエミツタ領域15即ちセンサー電極16の端 子Sには、接合Je に逆バイアスを与える所定の

斯くすると第6図Aに示すPNPトランジスタ の断面に於ける電位分布は、第6図Bに示す如く なり、撮像光学像による光照射によつて生じたキ ヤリア即ちホール及び電子のうちホールe+は端 1に対する光は少なくとも電極13とこれの下の 10 子C側に流れて消滅するが、電子e一はペース領 域6に蓄積される。この場合、或る量以上の電荷 e 一が蓄積されると接合Je が順バイアスとなり、 この或る量以上の電荷即ち電子はエミツタ側にオ ーバーフローする。

そして、との光感知部1のペース領域6に蓄積 された電荷を例えば帰線消去期間に於いてシフト レジスタ2の転送部7に転送する。この転送は、 通常の如くセンサー電極16に対し転送電極11 に所要の負の電位を与えることによつて転送部7 20 にポテンシャル井戸を形成してその転送を行う。 その後はこのシフトレジスタ2に於いて第1図に 説明したように各転送部了の電荷を垂直方向に順 次シフトさせる。このシフトは通常の如く転送電 極11にクロツク電圧を与えて行う。そしてこの た多結晶シリコン層より成る領域15を窓14を 25 間、即ち転送期間中に前述したと同様に撮像光学

た多結晶シリコン層より成る領域15を窓14を 25 通じて光感知部1の半導体層6上に被着生成させ てPN接合を形成するようになすこともできるし、 或いは第5図に示す如く光感知部1の半導体領域 6上に選択的に領域6と異なる導電型の不純物を 例えばイオン注入法或いは拡散法によつてドーブ 30 頭に述べたようにセンサー電極を構成する多結晶 し、P型の領域15を形成して接合Jeを形成す るようになすこともできる。第5図に於いて16 は領域15の一部にオーミツクに被着した電極即 ちセンサー電極で、第4図の例では領域15自体 をいわばセンサー電極とした場合である。

斯くして光感知部1に、接合Je をエミツタ接 合とし、半導体領域5及び6間に形成されるPN 接合Jc をコレクタ接合とするトランジスタ、即 ち領域15,6及び5を夫々エミツタ、ペース及 びコレクタの各領域とするPNPトランジスタを 40 構成する。

このような構成に於いて、半導体領域5即ちシ フトレジスタ2の基体領域となり前述のトランジ スタのコレクタ領域となる領域5の端子Cに正の 間、即ち転送期間中に前述したと同様に撮像光学 像による受光をなす。

上述の本発明装置によれば、その光感知部1を 構成するトランジスタのエミツタ領域15に於い て直接的に受光がなされるようになしたので、冒

シリコンを通じて更にその下の絶縁膜を介して受 光をなす場合の感度に比し特に短波長側の感度の 向上を図ることができるものである。

更に本発明装置によれば、或る以上に生じた電 35 荷をオーバーフローし得るものであるから従来の もののようにオーバーフロードレインを特設する 必要がなく、更にセンサー電極に与える電位によ つてオーバーフローの生じ始める電荷量を調整設 定できる利益もある。

尚、接合Je としては種々の構成をとり得、へ テロ接合、ショツトキー障壁による構成をとるこ ともできる。又、各部の導電型を図示とは逆導電 型とするなど種々の変更をなし得ることは明らか であろう。

#### <sup>12</sup>特許公報<sup>(B2)</sup>昭58-46905

(3)

5

特公 昭58-46905

5

#### 図面の簡単な説明

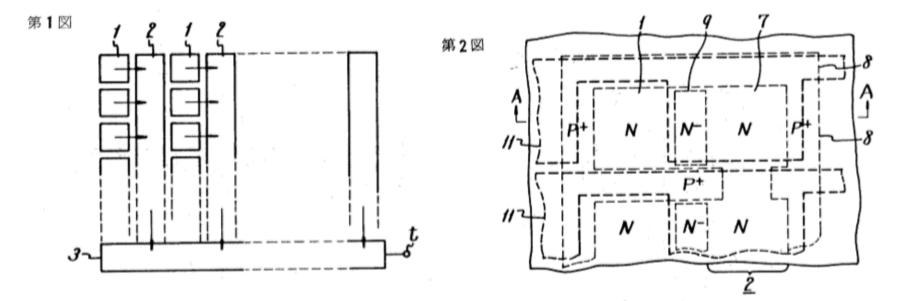

第1図は本発明の説明に供する固体撮像装置の 構成図、第2図はその要部の拡大平面図、第3図 はそのA-A線上断面図、第4図は本発明装置の 一例の要部の拡大断面図、第5図は本発明装置の 他の例の要部の拡大断面図、第6図は本発明装置 6

の動作の説明図である。

4は半導体基体、1は光感知部、2はシフトレ ジスタ、5及び6は半導体領域、8はチャンネル ストツバー領域、9は障壁領域、15はエミツタ 領域、16はセンサー電極、Je及びJcは接合 である。

#### Fig.1 Top View of Conventional Interline Transfer CCD Image Sensor

Fig.2 Top View of Conventional Interline Transfer CCD Image Sensor Picture Element Cell

Visit https://www.j-platpat.inpit.go.jp/ and type Japanese Patent Number 1975-134985

#### 図面の簡単な説明

第1図は本発明の説明に供する固体撮像装置の 構成図、第2図はその要部の拡大平面図、第3図 はそのA-A線上断面図、第4図は本発明装置の 一例の要部の拡大断面図、第5図は本発明装置の 他の例の要部の拡大断面図、第6図は本発明装置 の動作の説明図である。 電荷転送部 (CTD) が形成される面を主面と呼ぶ。図(6)は 受光面は主面側でも裏面側でも 特許請求範囲に入る。主面が シリコンウェハー上部でも下部 裏面でも特許請求範囲に入る。

図(6)はより一般に適応される。

第4図は本発明装置の一例の要部の拡大断面図、 第5図は本発明装置の他の例の要部の拡大断面図、 第6図は本発明装置の動作の説明図である。

Fig.6 shows that this is also the invention of in pixel VOD (vertical overflow drain). Visit https://www.j-platpat.inpit.go.jp/ and type Japanese Patent Number 1975-134985

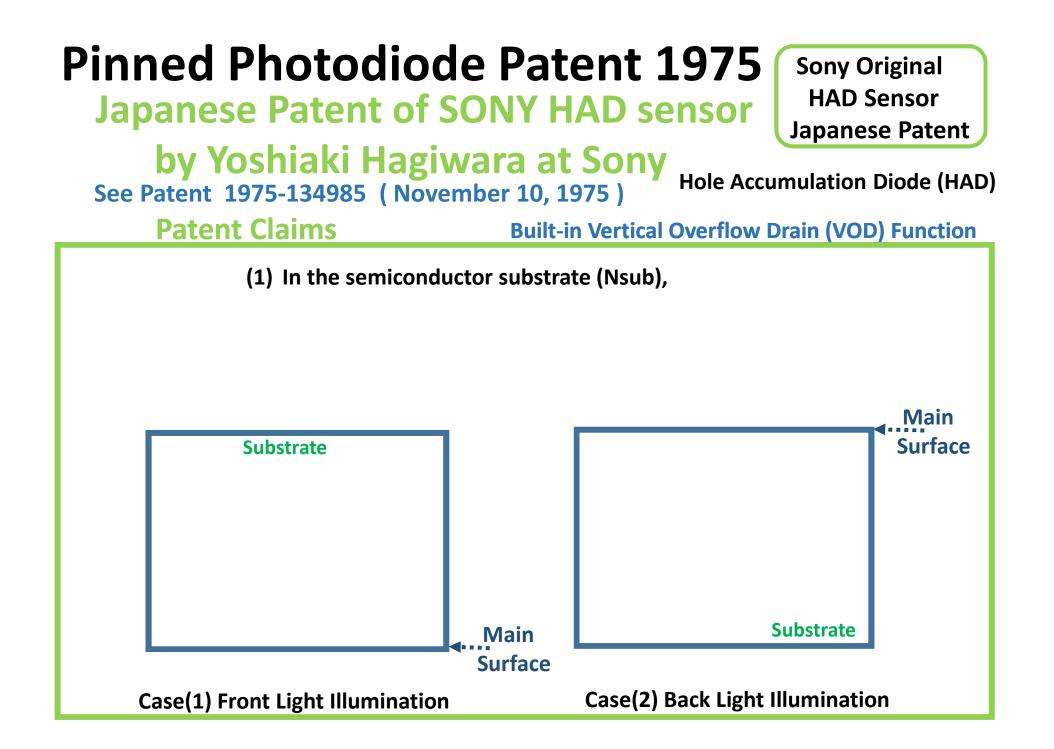

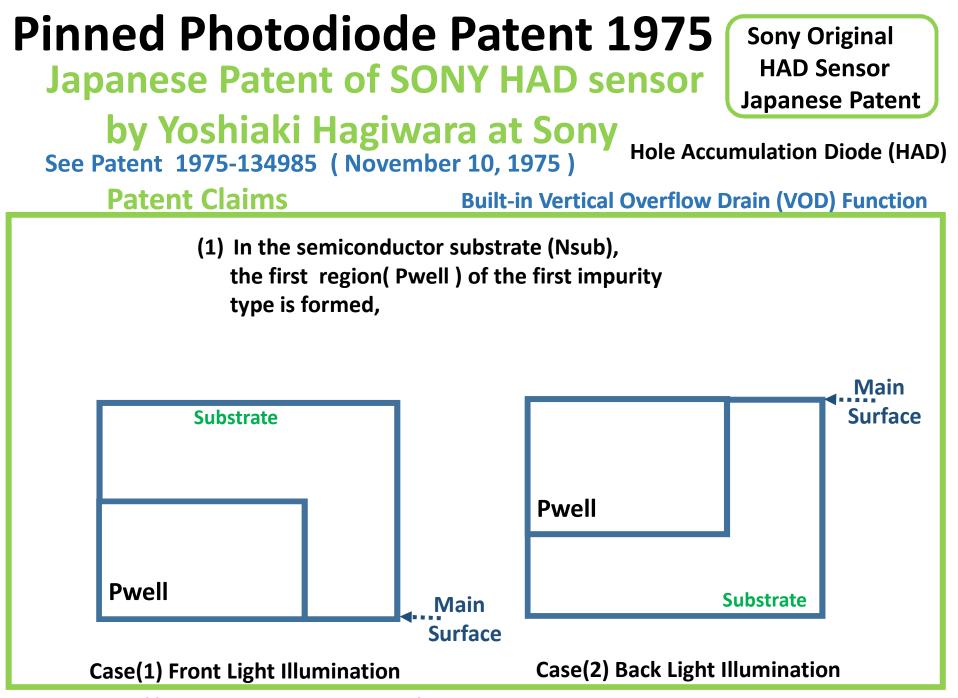

## **Pinned Photodiode Patent 1975**

**Japanese Patent of SONY HAD sensor**

by Yoshiaki Hagiwara at Sony

Sony Original HAD Sensor Japanese Patent

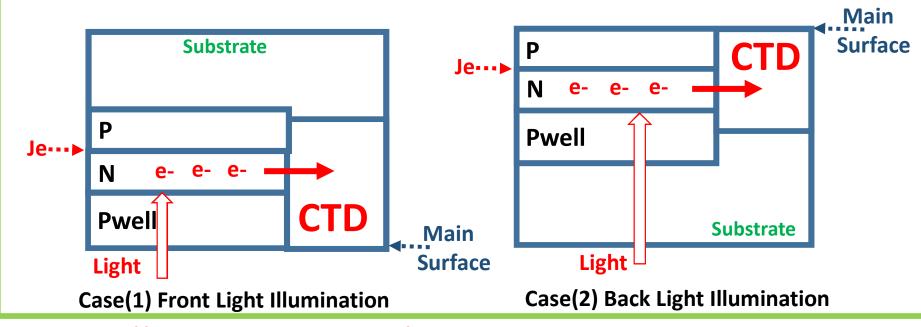

See Patent 1975-134985 (November 10, 1975) Patent Claims (2) on which, the second region (N) of the second impurity type is formed. Hole Accumulation Diode (HAD) Built-in Vertical Overflow Drain (VOD) Function

# **Pinned Photodiode Patent 1975**

**Japanese Patent of SONY HAD sensor**

by Yoshiaki Hagiwara at Sony

Sony Original HAD Sensor Japanese Patent

See Patent 1975-134985 (November 10, 1975) Hole Accumulation Diode (HAD)

Patent Claims

**Built-in Vertical Overflow Drain (VOD) Function**

(3) The charge (e-) from the light collecting part (N/Pwell Junction ) is transferred to the adjacent charge transfer device (CTD).

(4) Both are placed along the main surface of the semiconductor substrate.

## **Pinned Photodiode Patent 1975**

**Japanese Patent of SONY HAD sensor**

by Yoshiaki Hagiwara at Sony

Sony Original HAD Sensor Japanese Patent

Hole Accumulation Diode (HAD)

See Patent 1975-134985 (November 10, 1975)

**Patent Claims**

**Built-in Vertical Overflow Drain (VOD) Function**

(5) In the solid stare image sensor so defined, a rectifying Emitter junction (Je) is formed on the second region (N) of the light collecting part (N/Pwell),